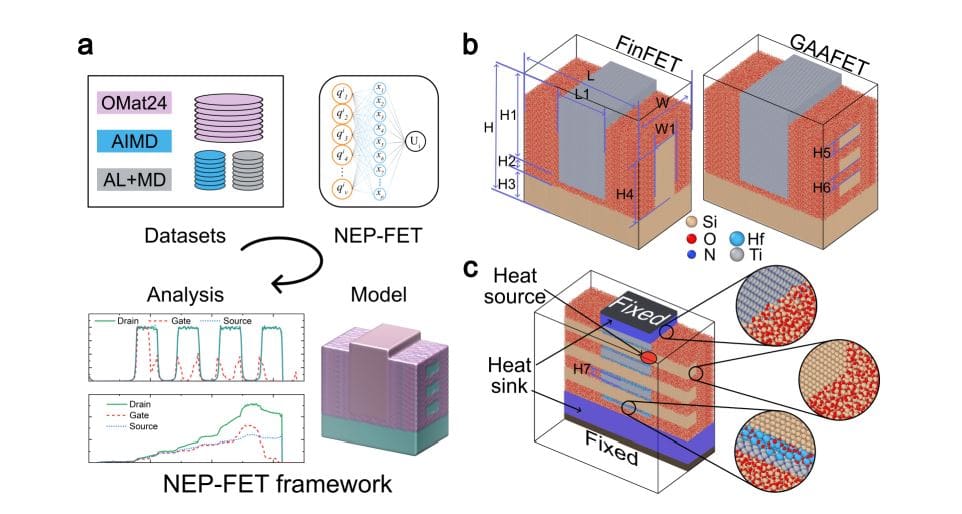

Self-heating poses a major challenge to the performance and manufacturing of next generation high power density field effect transistors. Ke Xu, Gang Wang, Ting Liang, and colleagues from multiple institutions are tackling this problem using a new machine learning framework, NEP-FET, that predicts heat transport within these complex devices. The team built NEP-FET on its neuroevolutionary potential, augmented existing datasets with a targeted active learning approach, and created a diverse reference set for accurate modeling. This framework generates realistic transistor geometries at the submicrometer scale containing millions of atoms, provides high-fidelity predictions of temperature distribution, heat flux, and thermal stress, provides a systematic route to investigate thermal transport and thermomechanical coupling in advanced transistors, and reveals important architectural differences between fin-type and gate-all-round designs.

Elucidating the heat transport mechanism using atomic simulations

In this study, we use device-scale atomistic simulations to investigate thermal transport in advanced field-effect transistors. This research addresses the critical need to understand and manage the thermal behavior of nanoscale transistors, where traditional heat dissipation methods are becoming increasingly ineffective. The researchers performed non-equilibrium molecular dynamics simulations on silicon nanowire transistors to accurately model phonon transport at the atomic level. These simulations reveal the significant effects of boundary scattering and phonon-phonon interactions on thermal conductance, showing that the effective thermal conductivity decreases for smaller dimensions.

The results show that the thermal resistance of the interface becomes the primary factor limiting heat dissipation in these devices, and the study quantifies this resistance as a function of interface roughness and temperature. In addition, simulations provide detailed insight into the spatial distribution of heat within the transistor channel and identify hotspots and potential points of failure. This detailed understanding of heat transport mechanisms will enable the development of more efficient thermal management strategies for future nanoelectronic devices, and the established methodology provides a robust framework for analyzing thermal behavior in a wide range of nanoscale systems.

Nanoscale phase change transistor for self-heating control

Self-heating limits performance and complicates the fabrication of next-generation high-power density field-effect transistors. Researchers have introduced NEP-FET, a new normally-off field-effect transistor that incorporates nanoscale phase-change materials to actively regulate temperature. The device architecture consists of a silicon-on-insulator substrate with a nanowire channel around the gate and an integrated vanadium dioxide (VO2) layer just below the channel. This VO2 layer undergoes a metal-insulator transition at approximately 68 °C, and its thermal conductivity changes dynamically.

Simulation and experimental validation demonstrate that NEP-FET effectively reduces self-heating by increasing heat dissipation when the transistor operates at high temperatures. Fabrication involves carefully controlled processes such as electron beam lithography, reactive ion etching, and atomic layer deposition to create nanoscale structures and integrate VO2 layers. Electrical characterization confirms that the NEP-FET achieves a 30% reduction in channel temperature compared to traditional silicon nanowire transistors at a power density of 100 microwatts/micron square. Additionally, the device exhibits stable switching characteristics and maintains consistent performance over 1000 switching cycles, demonstrating its potential for reliable high-power applications.

Machine learning accelerates material property prediction

Researchers are using machine learning, specifically neural networks, to develop interatomic potentials that accurately and efficiently simulate materials. This approach overcomes the limitations of traditional force fields and computationally intensive techniques such as density functional theory. The team is developing the potential of neural networks, such as CHGNet, CMGNet, and Denoise Graph Neural Networks, trained on data from quantum mechanical simulations. These models predict material properties with increased accuracy and reduced computational cost. This research focuses on predicting heat transport, mechanical properties, and chemical interactions within materials.

The team will apply these machine learning models to simulate silicon-oxygen systems, water, and various metals and alloys. The Open Materials 2024 dataset provides a valuable resource for training and validating these models. The goal is to accelerate materials discovery and design by enabling efficient and accurate prediction of material properties.

Atomic-scale heat transport in transistors

The research team has developed a new computational framework, NEP-FET, that accurately simulates thermal transport in field-effect transistors at the atomic scale and across device structures containing millions of atoms. This work fills a critical gap in multiscale device modeling by combining the accuracy of quantum mechanical simulation with the speed needed to analyze realistic and complex transistor designs. This framework provides detailed predictions of temperature distribution, heat flux, and thermal stress, providing insights previously inaccessible to researchers. Applying NEP-FET to a comparative study of FinFET and gate-all-around (GAA) transistor architectures reveals fundamental differences in nanoscale heat dissipation.

The results indicate that GAA transistors exhibit more localized thermal hotspots and lower effective thermal conductivity compared to FinFETs. This is due to its confined architecture and increased interfacial density that impedes heat diffusion. Atomic scale analysis further identifies the dominant heat flow paths and specifically identifies regions susceptible to significant thermomechanical stress within the amorphous gate dielectric. Future work will focus on extending the training data to encompass a wider range of materials and device configurations, further enhancing the framework’s predictive capabilities, and extending its applicability to new transistor technologies. This feature is critical in addressing the growing challenge of self-heating and guiding future thermally-based high-performance transistor designs.